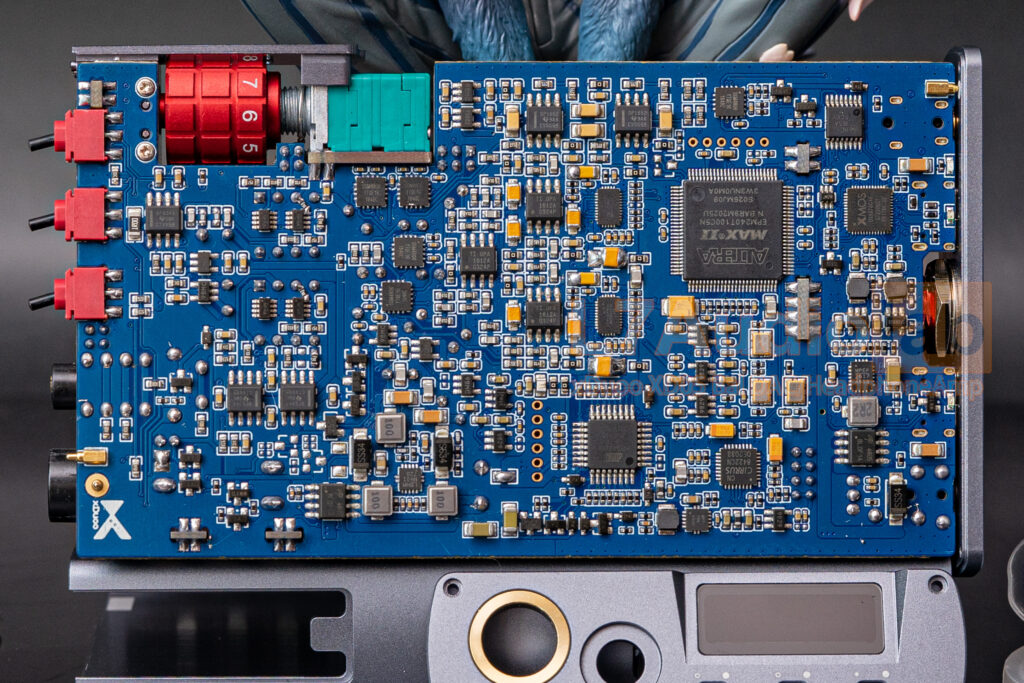

刚刚测完xDuoo XD-05 BAL的USB输入之后,我一直有点头疼……这到底是在DAC部分出了问题还是全部都出了问题?以我对乂度的感觉,应该不至于……为此我有点夜不能寐……然后我看着电路板……傻气一冒!决定利用它的AUXin功能先把模拟部分测个七七八八!

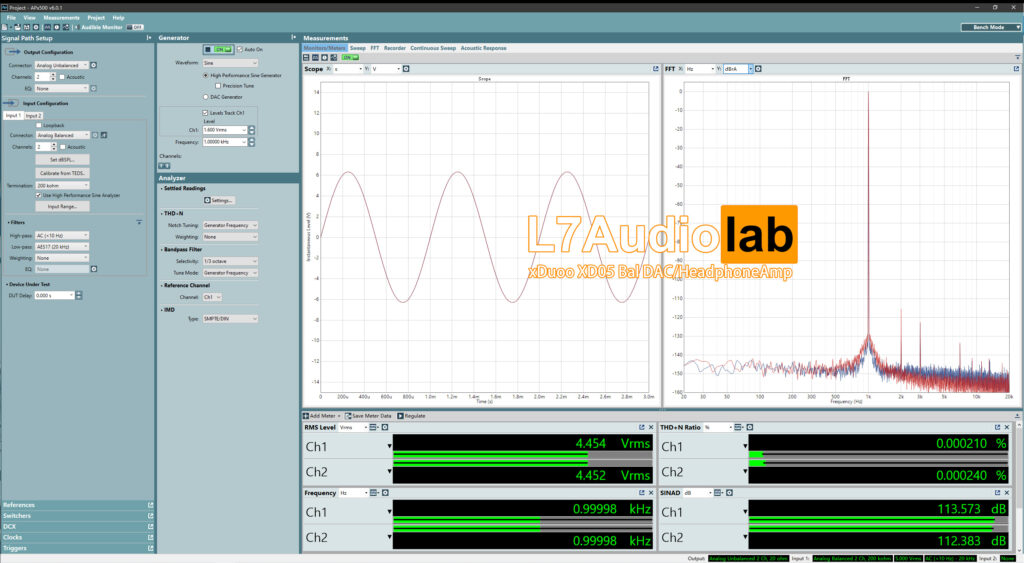

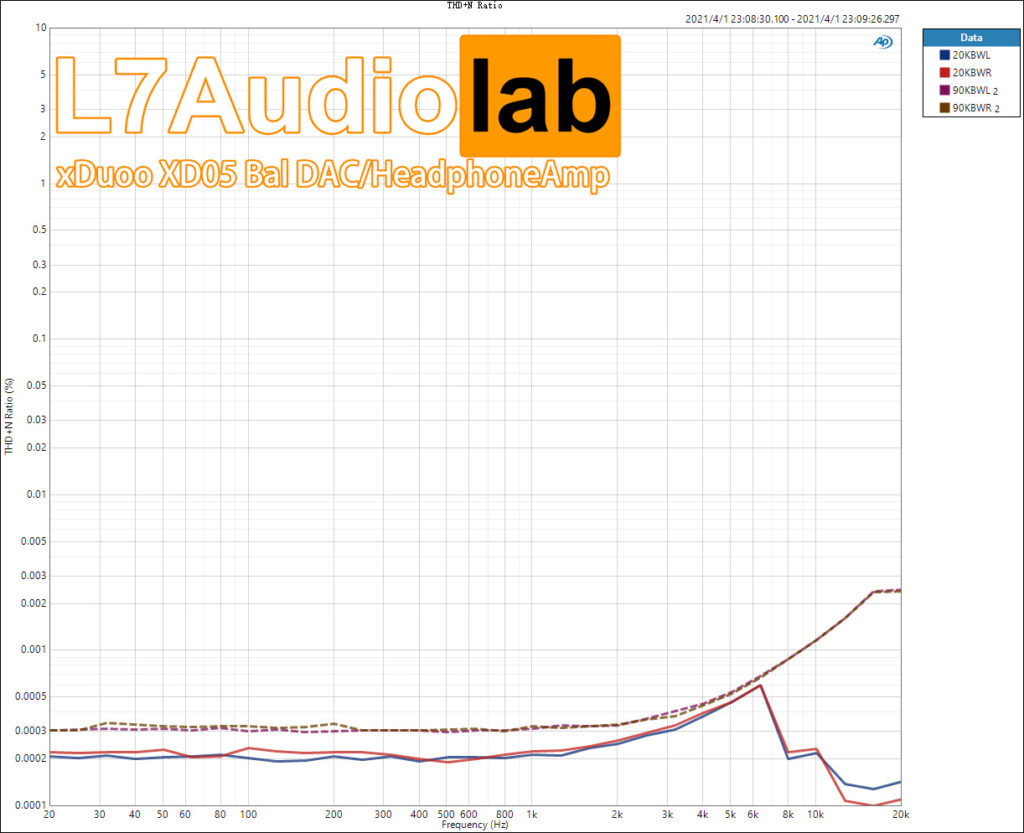

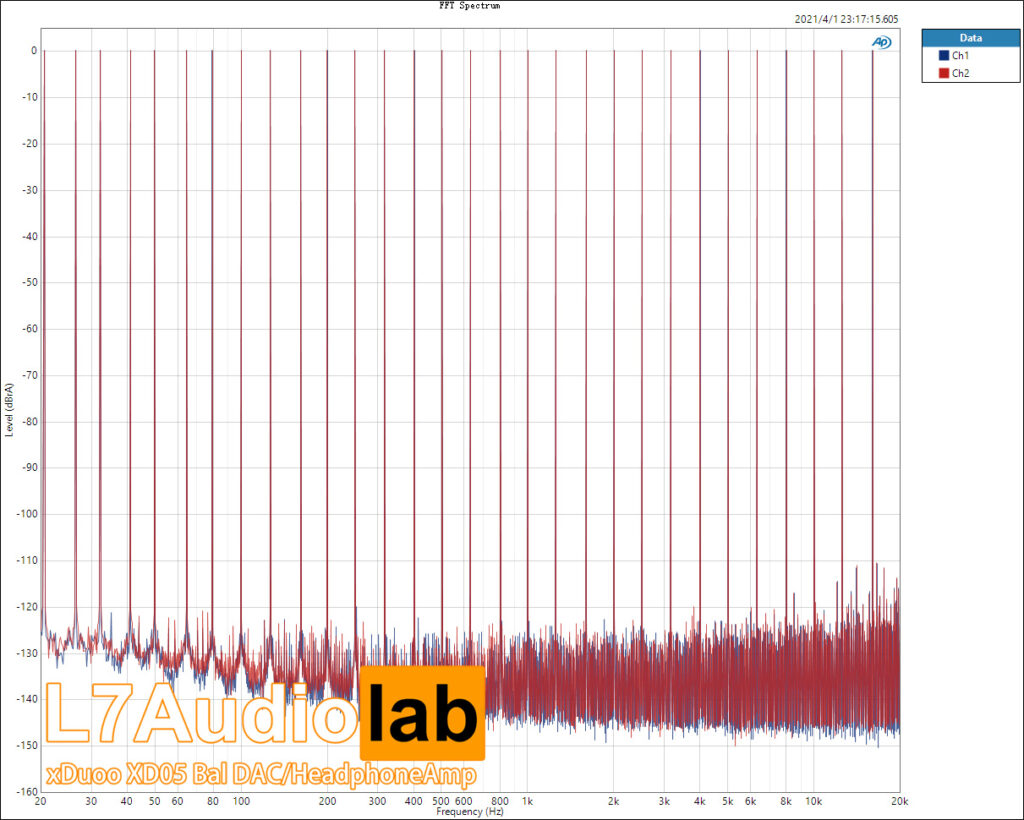

我们首先大概测一下4V输出的仪表板:

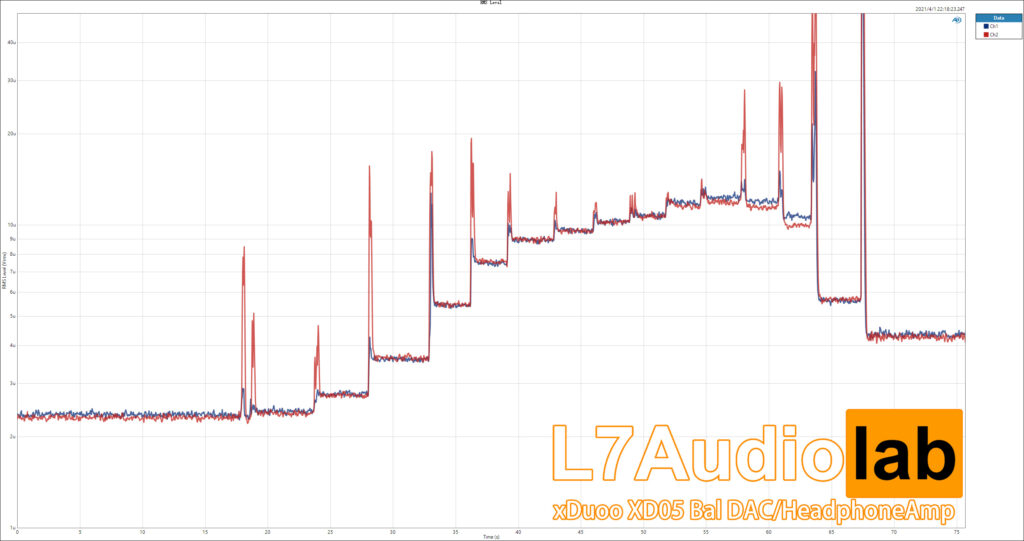

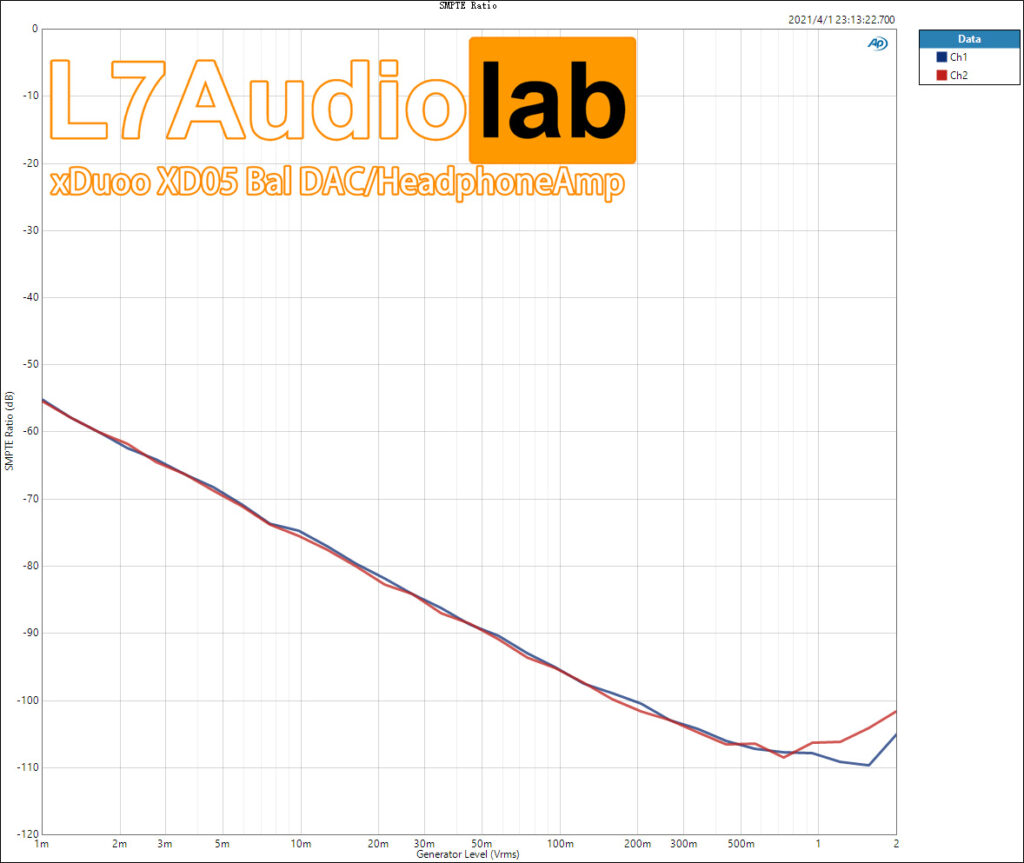

蛤?看来性能还是不错的啊!因为一些特别的原因,莫名其妙测成了4.4V……(其实还是懒)本来最理想是用2V进 4V出的……但是……遇到了问题:我调整音量旋钮的时候,系统的底噪有着明显的变化(于是我单独测了下面这个图 横轴是我音量旋钮从最小拧到最大的过程,纵轴是底噪)

我印象当中这是一个设计问题,但是由于我才疏学浅什么都不懂的……于是去请教了专业的大佬。

大佬是这样说的:

用叠加原理,从运放+端看出去的等效源阻抗,其实是那个电位器上下两部分并联

当电位器处于中间位置时,等效源阻抗最大

这个时候,如果电位器电阻太高,运放电流噪声又很大,就翻车了嘛

然后很多瞎设计又喜欢把增益搞贼大,结果就是信号增益小于0,噪声增益大于0

这种脑溢血设计……

好吧,我承认我疏忽了……常年看数0机的设计没想到这种上上上个世代的设计依然存在……于是我干脆把音量打到最大进行测量……

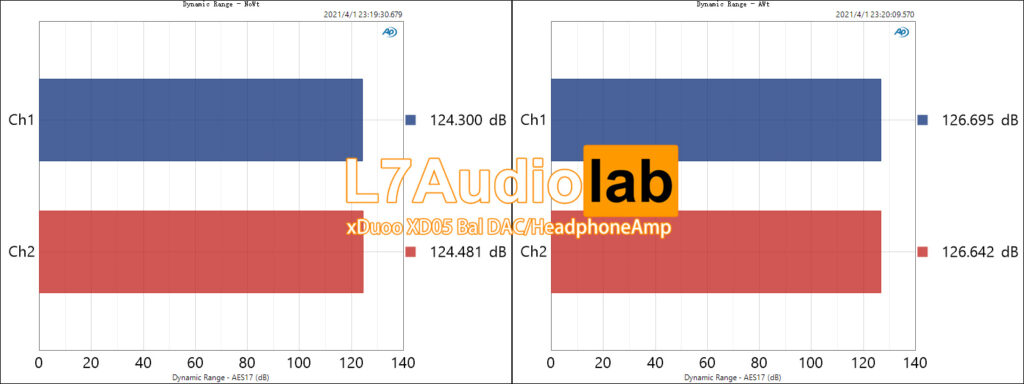

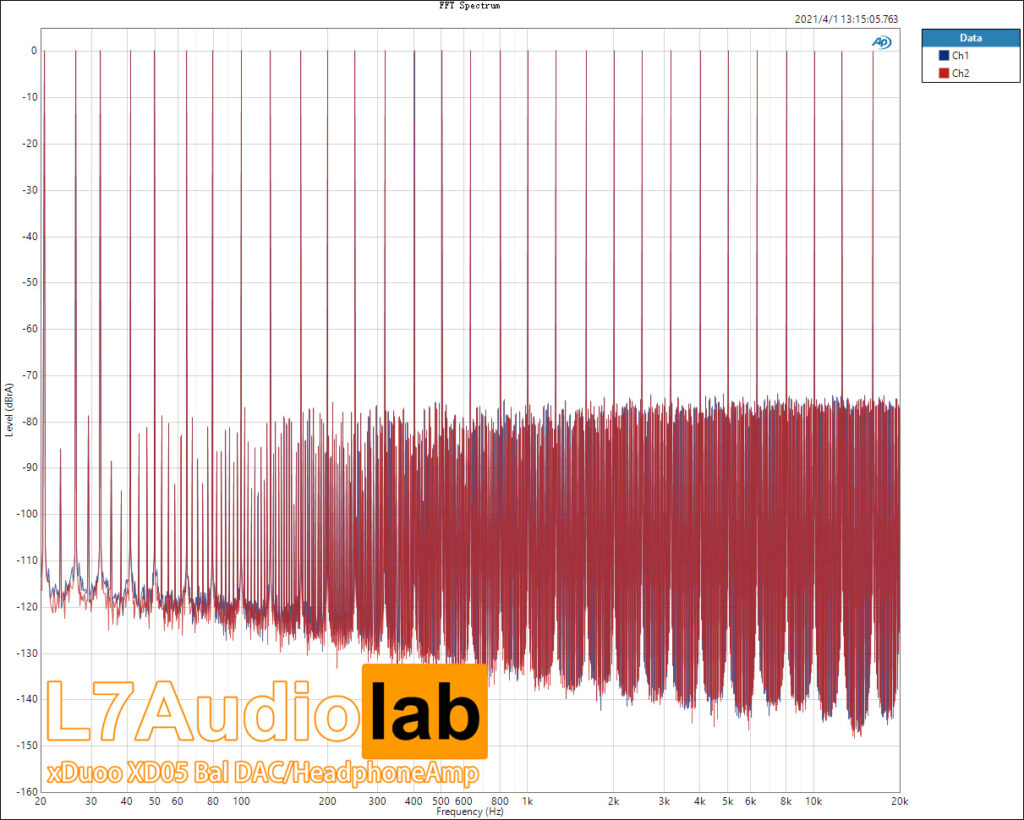

!!!!!!!!!!!!!!!!!!这模拟部分的性能……不差啊!看来就是数字部分和DAC部分的问题了……以我粗浅的知识来看……基本上主要问题出在9038Q2M附近的那一堆MLCC上面……众所周知X7R甚至更低级的MLCC有着明显的压电效应……会导致之前测量里面那样的多音…… 乂度赶紧换了吧……回头是岸啊……

第一!

狼教授不按套路来,还有part2。

不仅免费测试,还要治病救人 https://tb2.bdstatic.com/tb/editor/images/face/i_f25.png

看到这个,有点小小欣慰。

PS,都爱用CPLD,为什么,显得专业,可以赋予各种技术说法。

支持国货,看IBASSO使用国产CPLD,也跟进。PS,

国货CPLD也是出自LATTICE,如同东莞AP,没有什么丢人,学习别人的技术做自己的东西。

国产CPLD的技术其实并不是出自LATTICE,是十年前一个国内做FPGA的公司SiliconBlue(创始人和研发基本是国人)被LATTICE收购了,但是很多研发大牛就出来了分为好几拔搞自己的国产FPGA。